LambdaConcept experts design proven and reliable FPGA based systems

Rather than directly using VHDL and Verilog to build our projects, most of our work is based on next generation hardware construction languages such as (n)Migen and cores libraries MiSoC/Litex.

These new design techniques support highly parameterized generators and profit from dynamic and metaprogramming features of the underlying Python language, allowing us to create modular and scalable FPGA based systems.

We are experts in using Xilinx, Lattice, and Altera devices.

Some of our work

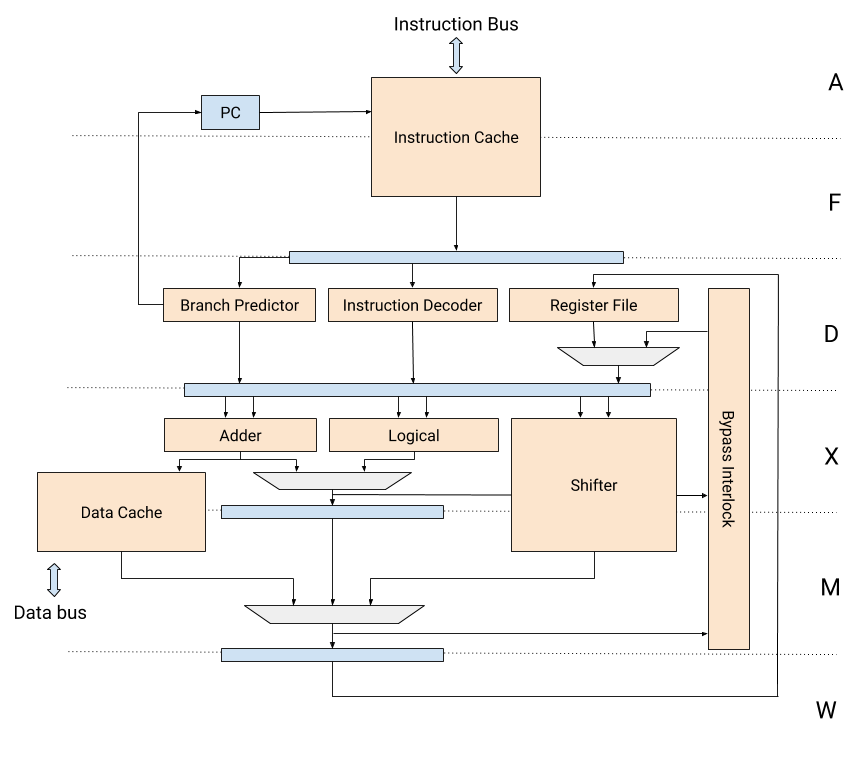

Minerva 32-bit RISC-V soft processor:

Minerva is a CPU core that currently implements the RISC-V RV32I instruction set. Its microarchitecture is described in plain Python code using the nMigen toolbox.

Minerva is pipelined on 6 stages:

- Address The address of the next instruction is calculated and sent to the instruction cache.

- Fetch The instruction is read from memory.

- Decode The instruction is decoded, and operands are either fetched from the register file or bypassed from the pipeline. Branches are predicted by the static branch predictor.

- Execute Simple instructions such as arithmetic and logical operations are completed at this stage.

- Memory More complicated instructions such as loads, stores and shifts require a second execution stage.

- Writeback Results produced by the instructions are written back to the register file.

View Minerva on Github

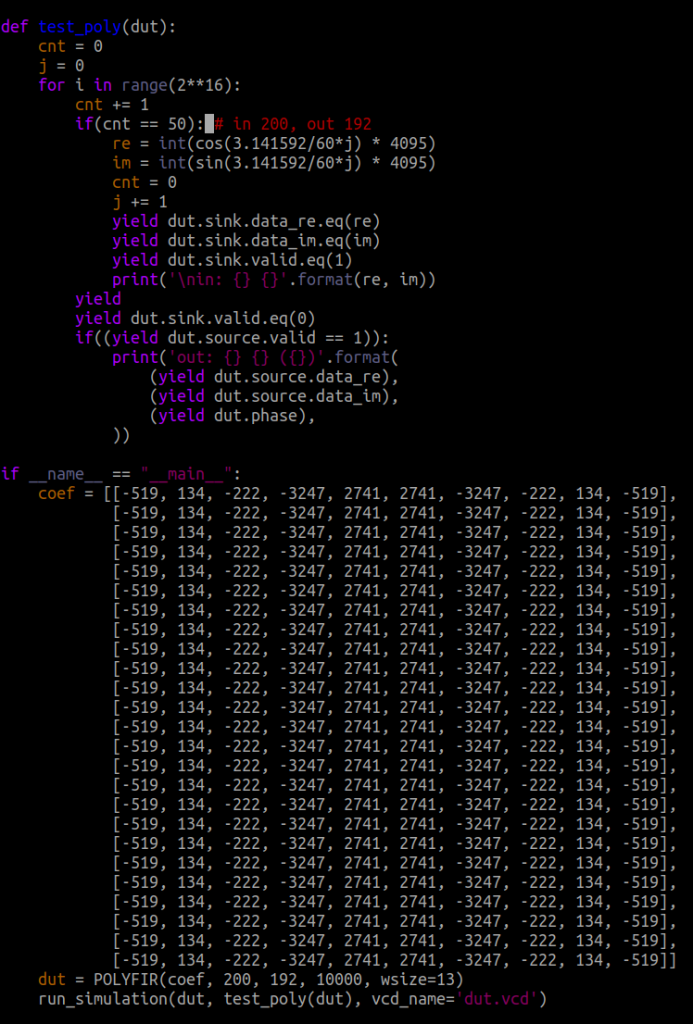

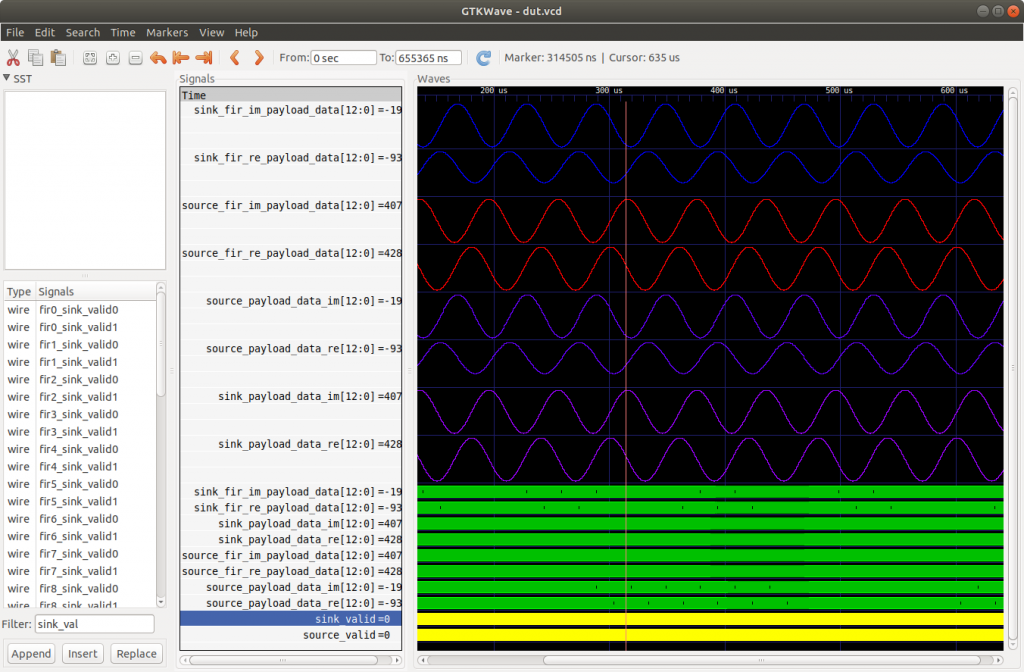

Poly-FIR:

The polyphase decomposition of the sampled data and filters allows efficient resampler architectures to be designed and implemented in hardware.

LiteSDCard:

LiteSDCard is a small footprint and configurable SDCard core developed jointly with Enjoy-Digital

PHY

- Xilinx Spartan 6 and 7-Series FPGA

- optional clock feedback (UHS-I)

Core

- Command & Data CRC inserters/checkers

- Single and multiple blocks write/read

- Errors detection and reporting

- Dynamically configurable clock speed

Frontend

- Synthetizable BIST

- 32 <–> 8 bits stream converters

Performances

- Up to 55 MB/s W/R performance at 125 MHz

View LiteSDCard on Github

FT60x SuperSpeed USB3.0 PHY:

USB3.0 32 Bits PHY controller designed in Migen for FTDI FT60x USB3.0 SuperSpeed.

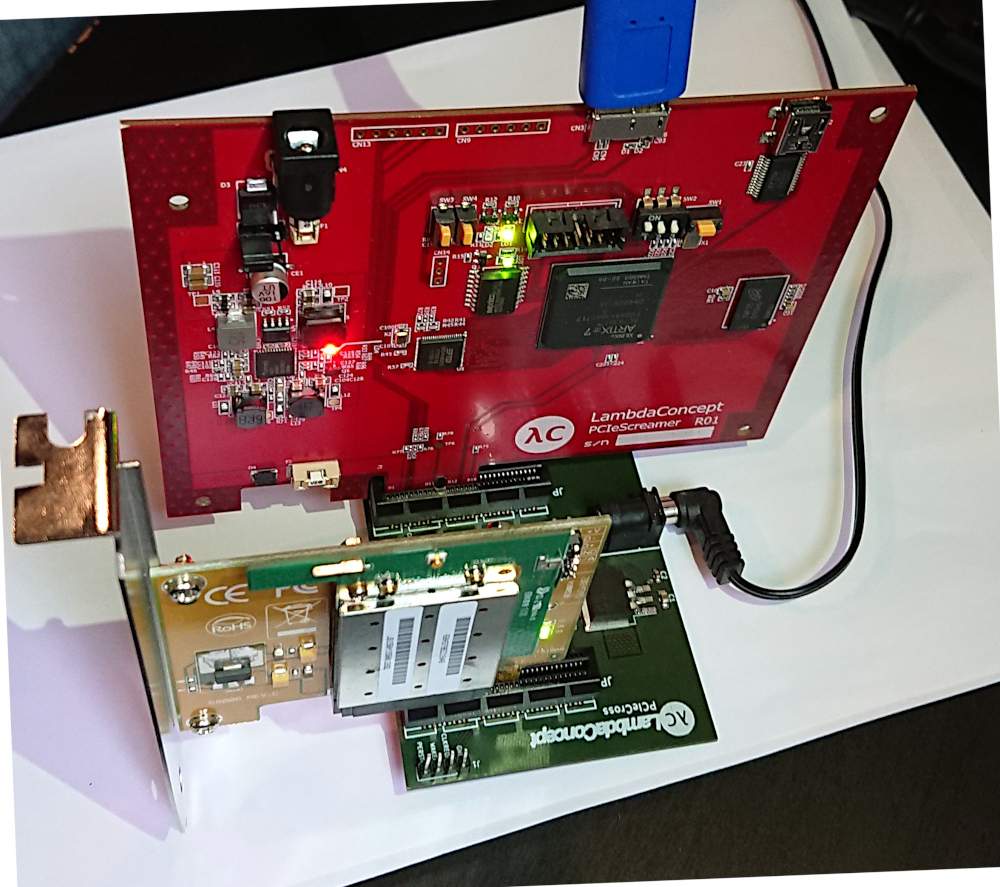

It currently supports FTDI mode FIFO245 up to 5Gbits/s and is actively used in PCIeScreamer and USBSniffer

View FT60x PHY on Github

ULPI USB2 PHY:

High Speed PHY controller designed for USB UTMI+ Low Pin Interface.

PHY

- Xilinx 7-Series FPGA

View ULPI PHY controller on Github